Nanotechnology

DOI: 10.1002/anie.200903583

## **Tube-in-Tube and Wire-in-Tube Nano Building Blocks: Towards the Realization of Multifunctional Nanoelectronic Devices\*\***

Moshit Ben Ishai and Fernando Patolsky\*

The design and rational synthesis of new nanoscale building blocks with well-defined chemical and physical properties is essential to bottom-up nanofabrication. One dimensional (1D) semiconductor nanostructures, nanowires, and nanotubes are viewed as potential basic building blocks for future applications<sup>[1-3]</sup> and have already been synthesized with a good control over their dimensions and chemical composition<sup>[4-6]</sup> and integrated into devices such as nanoscale fieldeffect transistors, piezoelectric generators, solar cells, energy storage devices, and biosensors.<sup>[7-11]</sup> However, the controlled synthesis of nanotubular materials of higher complexity remains a challenging and unexplored area of nanotechnology. Building additional functionality into nanotubes (NTs) during their synthesis may enable novel architectures and thus enhanced electronic and optoelectronic devices with diverse functions that are not possible with single-component nanotubes and nanowires. Semiconductor inorganic NTs have been synthesized in a number of ways; [12-15] however, none of the research performed to date has demonstrated the ability to design and prepare nanotubular structures with high structural and functional complexity.

We report herein on the formation and application of novel, entirely hollow, crystalline hybrid silicon nanotubular structures: tube-in-tube and wire-in-tube nanostructures (double-wall/multiwall NT-like structures), in which the chemical composition of each wall is independently defined, and the interwall distance and wall thickness can be precisely controlled. It should be noted that in contrast to existing inorganic multiwalled nanotubes, for which the interlayer distance is fixed and the composition of each wall cannot be individually controlled, the walls of our multiwalled Si nanotubes are well and controllably separated and can have different chemical composition and thicknesses, if so required.

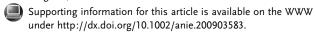

A schematic outline for the synthesis of the multiwall hybrid silicon nanotubular structures is depicted in Figure 1. The hybrid SiNTs were synthesized by using the rational growth of Ge(core)–Si–Ge (multishell) nanowire hetero-

<sup>[\*\*]</sup> We thank Dr. Alexander Sukernick for his help with e-beam writing experiments for the electrical devices preparation. This study was partially supported by the Israel Science Foundation (ISF), Legacy Program, Israel.

Figure 1. Synthetic process for silicon tube-in-tube nanostructures.

structures as a template. The growth of smooth germanium films on top of silicon substrates has proven to be a complex process involving different factors such as growth direction, surface faceting, germane (GeH<sub>4</sub>) partial pressure, and deposition temperature. The relatively large lattice mismatch between germanium and silicon (ca. 4.2%) places very strict limitations for achieving conformal, smooth germanium layers on silicon surfaces. As a result, the growth of germanium on silicon substrates first proceeds through a two-dimensional layer-by-layer mechanism (for only several monolayers), but as the total strain energy increases with thickening of the thin film, three-dimensional Stranski–Krastanov (S–K) islands form. [20–22]

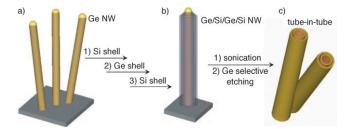

Preliminary results on the growth of germanium shells on silicon-nanowire cores were reported for the relatively high temperatures of 380 and 500 °C; however, these experiments were limited to a narrow range of core diameters and to certain shell thicknesses. [22-24] In contrast to the above growth methods, we undertook a systematic study of the growth conditions to form uniform and conformally smooth germanium shells, beyond the "critical thickness", on top of both silicon-core NWs and Ge-Si(core)-shell NWs in a layer-bylayer fashion, at a much lower deposition temperature of 330 °C, and a total growth pressure of 100 Torr. Notably, under these conditions, it is feasible to form conformal germanium shells of variable thicknesses, regardless of the initial core diameter, simply by adjusting the deposition time of the Ge shell (Figure 2a and Figure 1S in the Supporting Information). It is worth noting that at higher deposition temperatures of 380 and 500°C, and with similar shelldeposition time, germanium is preferentially deposited on the surface of the core-shell NWs to form a very rough layer and distinct three dimensional (3D) islands (Figure 2S in the Supporting Information). A representative high-resolution transmission electron microscopy (HRTEM) image of the Ge(core)-Si-Ge multishell (Figure 2a, left lower inset) reveals that the germanium-shell structure, before any annealing process is performed, shows no observable diffraction fringes. The ultralow-temperature deposition leads to

<sup>[\*]</sup> M. B. Ishai, Prof. F. Patolsky School of Chemistry The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University, Tel Aviv 69978 (Israel) E-mail: fernando@post.tau.ac.il

## **Communications**

Figure 2. a) Low-resolution TEM image of the Ge shell on a Ge(core)—Si(shell) nanowire at 330 °C. Scale bar: 200 nm. Insets: Low-magnification TEM image (top, scale bar: 230 nm) and HRTEM image (bottom, scale bar: 10 nm) of the amorphous Ge shell structure. b) Low- (scale bar: 200 nm) and high-resolution (inset, scale bar: 10 nm) TEM images of an annealed nanowire after a gradual temperature increase. c) Low-resolution TEM image after deposition of the Si shell on top of the annealed nanowire (b). Scale bar: 100 nm. Inset, top: HRTEM image of the corresponding sample, revealing a crystalline Si shell (scale bar: 5 nm).

shells of very poor crystallinity, thus enabling the formation of smooth, unstrained conformal layers of germanium.

The amorphous germanium shell can be crystallized by an in situ thermal-annealing step at 450 °C. However, the heating sequence procedure applied can strongly influence the structure of the germanium shells obtained. Stepwise heating (see experimental section in the Supporting Information) yields fully crystalline germanium shells, without affecting the integrity of the initial germanium shell (Figure 2b). HRTEM images recorded on the gradually annealed sample, as well as the corresponding fast Fourier transform (FFT) image (not shown), show that the Ge shell crystallizes to yield a singlecrystalline structure, and the measured spacing of the crystallographic (111) planes matched well with the 0.32 nm interplanar distance of germanium with a diamond-like structure. Alternatively, rapid continuous heating rates (>1 °Cs<sup>-1</sup>) lead to conversion of the smooth germanium shell structure into periodic crystalline islands (necklace-like structure; see Figure 3S in the Supporting Information). Finally, deposition of the Si shell on top of the previous Ge shell yields a single-crystalline Ge(core)-Si-Ge-Si (multishell) NW heterostructure, as confirmed by HRTEM micrographs and its FFT image (Figure 2c).

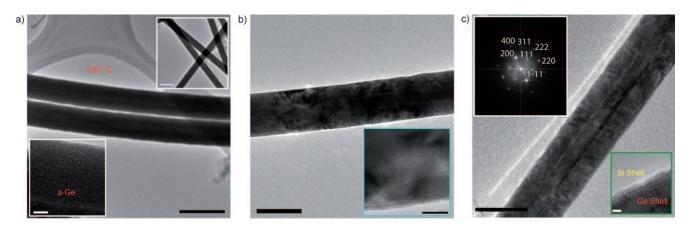

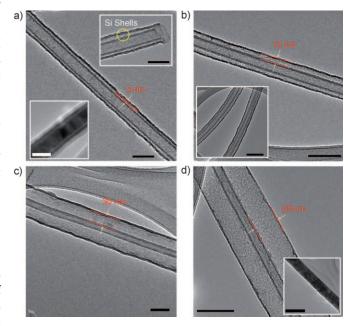

Selective extraction of the germanium core and shells from the heterostructures results in the formation of smooth,[15] uniform, and crystalline tube-in-tube structures with variable interwall distances of approximately 2, 10, 30, and 60 nm and a wall thickness of about 5 nm (Figure 3). The nanotubular structures are open-ended and possess wellseparated walls along nearly their entire length, probably as a result of electrostatic repulsion between the native oxidecovered neighboring walls. HRTEM studies and the corresponding FFT analysis reveal that the resultant DWSiNT-like structures (DWSiNT = double-wall silicon nanotube) have the cubic diamond structure of silicon (see Figure 4S in the Supporting Information). Furthermore, energy-dispersive Xray spectroscopy (EDX) spectra (see Figure 5S in the Supporting Information), which are common to all of the nanotubular structures in this work, show less than 1%

germanium impurities and have a well-correlated silicon signal along the longitudinal axis of the NT. This result further confirms the successful preparation of the DWSiNT-like structure.

Figure 3. a) Low-resolution TEM image of a DWSiNT-like structure with an interwall distance of approximately 2 nm. Scale bar: 50 nm. Bottom inset: TEM image of the core—multishell structure (scale bar: 40 nm). Upper inset: High-magnification of the open-ended nanotube. The yellow circle highlights the walls of the nanotubular structure; scale bar: 50 nm. b) Low-resolution TEM image of a DWSiNT-like structure with an interwall distance of approximately 10 nm. Scale bar: 100 nm. Inset: Low-resolution TEM image of DWSiNT-like structures with a Ge core size of around 10 nm. Scale bar: 100 nm. c) Low-resolution TEM image of a DWSiNT-like structure with an interwall distance of approximately 30 nm. Scale bar: 60 nm. d) Low-resolution TEM image of a DWSiNT-like structure with an interwall distance of approximately 60 nm. Scale bar: 100 nm. Inset: Low-resolution image of the corresponding template. Scale bar: 200 nm.

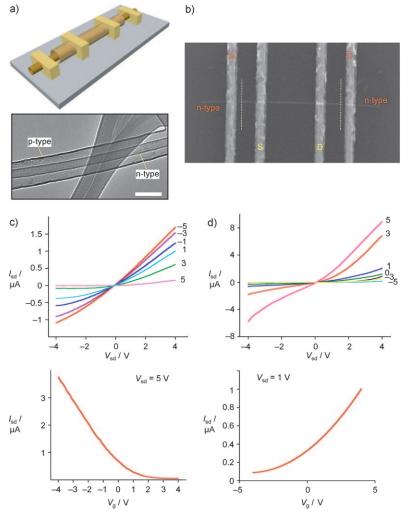

A unique advantage of our synthetic approach is that it enables us to control precisely the chemical composition of each wall of the NTs. Specifically, DWSiNTs with an exterior n-type wall and an interior p-type wall (Figure 4a) were synthesized with the use of phosphine (PH<sub>3</sub>) and diborane (B<sub>2</sub>H<sub>6</sub>) dopants, respectively, to give nanotubular structures with dual electrical properties. Notably, we used the synthesized n-type@p-type DWSiNTs (Figure 4a) to form dual-functionality field-effect transistors (Figure 4b). This is first demonstration of controlled doping of individual walls in any type of multiwalled nanotubular structure and the characterization of the electrical properties of the doped walls using electrical transport measurements. In these measurements, a back-gate electrode was used to modulate the electrostatic potential of the double-walled nanotubular structure while the current versus voltage for each wall was measured separately. Gate-dependent, two-terminal electrical measurements (Figure 4c,d) clearly demonstrate that the boron-doped (B-doped) and phosphorusdoped (P-doped) walls of the double-walled silicon nanotube structure behave as p- and ntype electrical elements. The p- and n-type walls yield average transconductance values of 700 and 520 nS, respectively, at these specific doping levels (1:800 B/Si and 1:800 P/Si, respectively). Those values are comparable to the performance of silicon nanowires devices under similar experimental conditions. [25,26] Clearly, intriguing multifunctional electrical nanodevices of complex performance can be fabricated using a single nanotubular building block with a known number of electrically independent wall elements.

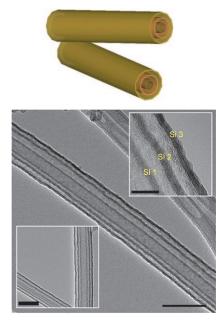

On the basis of our synthetic approach, we also formed multiwalled nanotubular structures. Figure 5 shows a representative low-resolution TEM image of a triple-walled nanotubular structure.

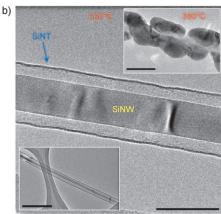

Our approach can be further extended to produce unique hybrid nanotubular structures: the so-called wire-in-tube nanostructures, as illustrated in Figure 6a. The first step is the formation of SiNW cores from gold nanocluster catalysts. This step was carried out with the use of a silane precursor at 460°C. Germanium was subsequently deposited on top of the silicon core at a temperature of 330 °C. To the best of our knowledge, this is the first report on the formation of uniform and smooth germanium shells on silicon NWs with no limiting dimensions (shell thickness and core diameter). The growth of germanium shells at higher temperatures follows an S-K mechanism to give well-separated 3D clusters (Figure 6b, top inset). Finally, a gradual increase of the temperature up to 450°C, followed by the growth of a conformal silicon shell at 450°C and selective etching of the germanium shell, led to the formation

Figure 4. a) Top: Schematic illustration of the silicon double-walled nanotube-based dual-transistor electrical device. Bottom: Low-resolution TEM image of the DWSiNTlike structure. Scale bar: 100 nm. b) SEM image of the double-walled n/p-type multifunctional FET; S = source, D = drain. c,d) Electrical measurements of dual-performance p@n-type nanotransistor devices fabricated from a p-type outer/n-type inner DWSiNT. The upper plots show current  $(I_{sd})$  versus voltage  $(V_{sd})$  recorded individually on the external p-type and the internal n-type silicon walls, at various gate voltages  $(V_g)$ . The lower plots show transconductance curves for the individual p-type and ntype walls of the double-wall tubular structure. c) Outer p-type wall FET. d) Inner n-type wall FET.  $I_{sd}$  = source-drain current,  $V_g$  = gate voltage,  $V_{sd}$  = source-drain voltage.

of SiNWs within SiNTs. Figure 6b shows representative lowresolution TEM images of a typical SiNW with diameters of 40 and 20 nm, respectively, within uniform and smooth SiNTs.

To summarize, we have synthesized two unique crystalline hybrid nanotubular structures. The first consists of entirely hollow, uniform, and well-separated tube-in-tube structures with variable and uniform interwall distances ranging from 2 to 60 nm. The walls of these nanotubular structures can be readily and differentially doped in situ to form nanotubular structures with multiple built-in electrical properties and a controlled number of walls. In addition, we have demonstrated for the first time the synthesis of wire-in-tube nanostructures. These unique nanotubular structures might open the opportunity to fabricate novel nanoscale electrical and

## **Communications**

Figure 5. Schematic illustration of a triple-walled nanotubular structure, and its corresponding low-resolution TEM image. Scale bar: 100 nm. Upper inset: High-magnification image of the nanotube walls. Scale bar: 20 nm. Bottom inset: Low-magnification image of triple-walled SiNTs. Scale bar: 100 nm.

Figure 6. a) Schematic illustration depicting the synthesis of silicon nanowires in nanotubes. b) Low-resolution TEM image of a silicon nanowire (80 nm in diameter) within a silicon nanotube. Scale bar: 140 nm. Bottom inset: Low-resolution TEM image of the hybrid nanowire-in-nanotube structure with a silicon nanowire of approximately 20 nm in diameter. Scale bar: 240 nm. Upper inset: Low-magnification TEM image taken after deposition of a Ge shell on top of the Si nanowire at a higher temperature of 380 °C. Scale bar: 75 nm.

optoelectrical devices, as exemplified in this work by the fabrication of novel FET devices with dual-electrical performance. These findings might also open up the possibility to fabricate new nanoscale devices of higher complexity based on this new family of intriguing building blocks that are not achievable with the use of currently known nanostructures.

Received: July 1, 2009

Published online: October 12, 2009

**Keywords:** germanium · nanotechnology · nanotubes · nanowires · silicon

- [1] W. Lu, C. M. Lieber, Nat. Mater. 2007, 6, 841-850.

- [2] P. J. Pauzauskie, P. Yang, Mater. Today 2006, 9, 36-45.

- [3] C. M. Lieber, Z. L. Wang, MRS Bull. 2007, 32, 99-108.

- [4] Y. Li, F. Qian, J. Xiang, C. M. Lieber, *Mater. Today* **2006**, *9*, 18–27.

- [5] K. A. Dick, K. Deppert, M. W. Larsson, T. Martensson, W. Seifert, L. R. Wallenberg, L. Samuelson, *Nat. Mater.* 2004, 3, 380–384.

- [6] J. Xiang, W. Lu, Y. J. Hu, Y. Wu, H. Yan, C. M. Lieber, *Nature* 2006, 441, 489–493.

- [7] J. Xiang, W. Lu, Y. Hu, Y. Wu, H. Yan, C. M. Lieber, *Nature* 2006, 441, 489–493.

- [8] Z. L. Wang, J. Song, Science 2006, 312, 242–246.

- [9] B. Tian, X. Zheng, T. J. Kempa, Y. Fang, N. Yu, G. Yu, J. Huang, C. M. Lieber, *Nature* **2007**, *449*, 885–890.

- [10] C. K. Chan, H. Peng, G., K. Mcilwrath, X. F. Zhang, R. A. Huggins, Y. Cui, *Nat. Nanotechnol.* 2008, 3, 31–35.

- [11] G. F. Zheng, F. Patolsky, Y. Cui, C. M. Lieber, *Nat. Biotechnol.* 2005, 23, 1294–1301.

- [12] R. Tenne, A. Zettle, Top. Appl. Phys. 2001, 80, 81-112.

- [13] C. R. Martin, Science 1996, 266, 1961-1966.

- [14] J. Goldberger, R. Fan, P. D. Yang, Acc. Chem. Res. **2006**, *39*, 239 248

- [15] M. Ben Ishai, F. Patolsky, J. Am. Chem. Soc. 2009, 131, 3679– 3689.

- [16] A. L. Kolesnikova, A. Romanov, Philos. Mag. Lett. 2004, 84, 501-506.

- [17] J. G. Fossum, W. Zhang, IEEE Trans. Electron Devices 2003, 50, 1042–1049.

- [18] J. Jung, M. L. Lee, S. Yu, E. A. Fitzgerald, A. Antoniadis, IEEE Electron Device Lett. 2003, 24, 460–462.

- [19] F. Schäffler, Semicond. Sci. Technol. 1997, 12, 1515-1549.

- [20] D. J. Eaglesham, M. Cerullo, Phys. Rev. Lett. 1990, 64, 1943– 1946.

- [21] Y.-W. Mo, D. E. Savage, B. S. Swartzentruber, M. G. Lagally, Phys. Rev. Lett. 1990, 65, 1020–1023.

- [22] L. Pan, K.-K. Lew, J. M. Redwing, E. C. Dickey, Nano Lett. 2005, 5, 1081 – 1085.

- [23] H. Wang, M. Upmanyu, C. V. Ciobanu, Nano Lett. 2008, 8, 4305 4309

- [24] L. J. Lauhon, M. S. Gudiksen, D. Wang, C. M. Lieber, *Nature* **2002**, *420*, 57–60.

- [25] Y. Cui, X. Duan, J. Hu, C. M. Lieber, J. Phys. Chem. B 2000, 104, 5213 – 5216.

- [26] G. F. Zheng, W. Lu, S. Jin, C. M. Lieber, Adv. Mater. 2004, 16, 1890–1894.